CPU 성능을 이야기할 때 클럭 속도나 코어 수는 쉽게 떠올리지만, 실제 체감 성능을 좌우하는 핵심 요소 중 하나는 캐시 라인(Cache Line) 입니다. 같은 연산을 수행하더라도 메모리 접근 방식에 따라 성능 차이가 크게 벌어지는 이유는, CPU가 데이터를 처리하는 최소 단위가 바이트가 아니라 캐시 라인이기 때문입니다. 이 글에서는 캐시 라인이 무엇인지부터, 왜 성능에 결정적인 영향을 주는지까지 구조적으로 살펴봅니다.

CPU는 왜 메모리를 직접 보지 않는가

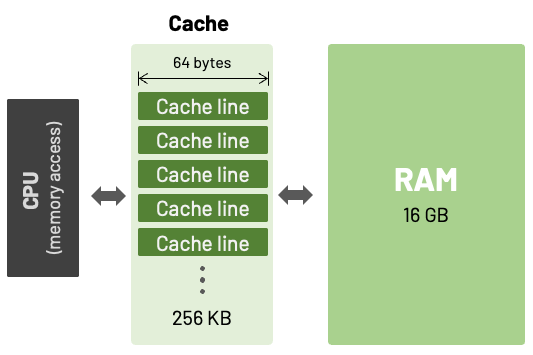

CPU와 메인 메모리 사이에는 근본적인 속도 차이가 존재합니다. CPU는 수 나노초 단위로 연산을 수행하지만, 메인 메모리는 그보다 훨씬 느린 속도로 동작합니다. 이 간극을 그대로 두면 CPU는 대부분의 시간을 메모리를 기다리는 데 쓰게 됩니다.

이를 해결하기 위해 CPU는 캐시(Cache) 라는 중간 저장소를 사용합니다. 자주 사용될 가능성이 높은 데이터를 미리 가져와 가까운 곳에 두고, 가능한 한 메모리 접근을 줄이는 구조입니다.

캐시 라인이란 무엇인가

캐시 라인은 CPU 캐시가 데이터를 저장하고 이동시키는 최소 단위입니다. CPU는 특정 변수 하나만 필요하더라도, 그 변수가 포함된 캐시 라인 전체를 메모리에서 가져옵니다. 일반적으로 캐시 라인의 크기는 64바이트이며, 이 크기는 대부분의 현대 CPU에서 공통적으로 사용됩니다.

즉, CPU 입장에서는

1바이트를 읽든

8바이트를 읽든

항상 64바이트 단위로 메모리를 다룬다는 의미입니다.

캐시 라인이 성능에 직접 영향을 주는 이유

캐시 라인이 중요한 이유는 CPU가 데이터를 “필요한 만큼만” 가져오지 않기 때문입니다. 항상 묶음 단위로 가져오기 때문에, 데이터 배치 방식이 성능에 직접적인 영향을 줍니다.

연속된 데이터가 같은 캐시 라인에 들어 있으면 한 번의 메모리 접근으로 여러 데이터를 동시에 사용할 수 있습니다. 반대로 필요한 데이터가 서로 다른 캐시 라인에 흩어져 있으면, 그만큼 캐시 미스가 늘어나고 CPU는 반복해서 메모리를 기다리게 됩니다.

공간 지역성과 캐시 라인

캐시 라인은 공간 지역성(spatial locality) 이라는 개념을 전제로 설계되어 있습니다. 프로그램이 어떤 메모리 주소를 접근하면, 그 주변 주소도 곧 접근할 가능성이 높다는 가정입니다.

예를 들어 배열을 순차적으로 접근하는 경우, 첫 요소를 읽을 때 이미 다음 여러 요소가 같은 캐시 라인에 함께 로드됩니다. 이 경우 이후 접근은 캐시 히트로 처리되어 매우 빠르게 실행됩니다. 반면, 배열을 불규칙하게 접근하면 매번 새로운 캐시 라인을 불러와야 하므로 성능이 급격히 떨어집니다.

캐시 미스와 지연 시간의 누적

캐시 라인이 맞지 않는 접근 패턴은 캐시 미스를 발생시킵니다. 캐시 미스가 발생하면 CPU는 다음 단계를 거칩니다.

L1 캐시 확인

L2 캐시 확인

L3 캐시 확인

메인 메모리 접근

이 과정은 단계마다 수십 배의 지연을 동반합니다. 연산 자체는 빠르지만, 캐시 미스가 반복되면 전체 실행 시간은 메모리 지연에 의해 지배됩니다. 그래서 CPU 성능 문제를 분석하다 보면, 연산량보다 메모리 접근 패턴이 병목이 되는 경우가 매우 많습니다.

캐시 라인과 false sharing 문제

멀티코어 환경에서는 캐시 라인이 또 다른 문제를 만듭니다. 서로 다른 스레드가 같은 캐시 라인에 포함된 서로 다른 변수를 수정하면, 실제로는 변수 공유가 없음에도 캐시 일관성 프로토콜이 계속 동작하게 됩니다. 이를 false sharing이라고 합니다.

false sharing이 발생하면

캐시 라인이 코어 간에 계속 무효화되고

불필요한 동기화 트래픽이 발생하며

CPU 사용률은 높지만 성능은 오히려 떨어지는 현상이 나타납니다.

이 문제 역시 캐시 라인이 최소 관리 단위이기 때문에 발생합니다.

데이터 정렬과 패딩의 중요성

성능을 고려한 코드에서는 캐시 라인 크기를 기준으로 데이터 구조를 설계합니다. 자주 접근하는 데이터는 같은 캐시 라인에 묶고, 멀티스레드에서 수정되는 데이터는 캐시 라인을 분리해 배치합니다.

이를 위해

구조체 필드 순서를 조정하거나

의도적으로 패딩을 넣어

캐시 라인 경계를 맞추는 기법이 사용됩니다.

이러한 설계는 연산을 줄이는 것이 아니라, 메모리 접근 비용을 줄이는 것에 초점을 둡니다.

CPU 캐시 라인은 성능 설계의 기준점이다

CPU 캐시 라인은 단순한 하드웨어 세부 사항이 아니라, 소프트웨어 성능을 좌우하는 기준 단위입니다. 알고리즘의 시간 복잡도가 같더라도, 캐시 라인을 고려했는지 여부에 따라 실제 성능은 크게 달라질 수 있습니다.

특히 대용량 데이터 처리, 서버 애플리케이션, 멀티스레드 환경에서는 캐시 라인을 이해하지 않고는 성능 문제를 정확히 진단하기 어렵습니다.

정리

CPU 캐시 라인이 성능에 영향을 주는 이유는, CPU가 데이터를 처리하는 최소 단위이기 때문입니다. 캐시 라인은 메모리 접근 횟수, 캐시 미스 발생 빈도, 멀티코어 간 동기화 비용까지 모두 좌우합니다. 결국 성능 최적화의 핵심은 연산을 줄이는 것이 아니라, 캐시 라인을 중심으로 메모리 접근을 설계하는 것이라고 볼 수 있습니다.